單片機在低頻信號頻率相位測量儀中的設計應用

頻率是信號的重要參數之一,如何獲得這一準確數據已經在信息領域顯得越來越重要了[1,2]。相位測量在信號提取、檢測、處理等方面有著重要的應用[3]。本設計采用89C52單片機和可編程邏輯器件(CPLD)為核心,利用單片機進行數據處理并顯示結果,軟件采用匯編語言實現,構成低頻信號頻率相位測量儀。 1系統工作原理 本設計以89C52單片機和可編程邏輯器件(CPLD)為核心,構成低頻信號頻率相位測量儀。該儀器具有移相、頻率和相位測量2大功能。移相電路由移相網絡和信號放大電路組成,對固定頻率信號(100 Hz,1 kHz,10 kHz)可滿足-45~ 45的相移要求;頻率、相位測量電路由阻抗變換電路、整形電路、分頻電路、計數器電路、鎖存器、數據處理和顯示電路等組成,可對10 Hz~20 kHz信號進行頻率和相位測量。單片機系統是整個硬件系統的核心,他既是協調整機工作的控制器,又是數據處理器,并完成對最終顯示的控制。 (1) 單片機89C52(內部帶8 kB FLASH ROM)、地址鎖存器74LS573和數據存儲器6264(內部 RAM為8 kB)構成的[4]。 (2) 數據處理主要是正確判斷對所輸入的信號是測頻還是測相,并完成測頻、測相的功能。 (3) 由控制面板、顯示接口芯片8279構成顯示電路。 2精度分析 本設計要求相位測量精度絕對誤差≤1?,因此,在所測信號一個周期中,只有計數數值超過360次時才能達到要求。對于被測信號頻率為20 kHz時,其周期為50 μs,在50 μs內計數值為360次,由此可計算出時間基準信號的頻率為20 kHz?360=7.2 MHz,所以采用8 MH z晶振作為時基信號源,完全可以滿足精度要求[5]。 3系統設計總框圖 系統設計總框圖如圖1所示。

4測頻、測相的實現 測頻、測相電路是本次設計的主要內容,此部分采用可編程邏輯器件(CPLD)完成,由單片 機控制。單片機的匯編程序就是按照CPLD的設計原理而編寫的[6,7]。

4測頻、測相的實現 測頻、測相電路是本次設計的主要內容,此部分采用可編程邏輯器件(CPLD)完成,由單片 機控制。單片機的匯編程序就是按照CPLD的設計原理而編寫的[6,7]。

圖2,圖3分別為測頻、測相的流程圖。為了便于說明,畫出此系統結構圖,如圖4所示。

CPLD電路描述:首先經過掃描P11控制74257(2選1)電路,選擇測頻還是測相,如果為高 電平則測頻,利用單片機產生10次中斷產生的秒信號,即在1 s中信號的脈沖數,其中計數器是由6個74193搭成的24位計數器,經鎖存器鎖存,等待單片機讀出;如果為低電平則測相。測相時先調用了測頻的程序但并不顯示,而是存起來待用,然后給D觸發器清零,否則得到的異或值不同,如圖3所示。a′,b′經過異或生成相位信號并發出中斷請求,與 8 MHz的時基信號相與所產生的脈沖由計數器計數,然后把所計的數送入鎖存器鎖存,等待單片機讀數。 5結語 本文采用單片機和可編程邏輯器件(CPLD)作為低頻數字相位測量儀的核心部分。用89C52進行數據控制、處理,送到顯示器顯示,硬件結構簡單,軟件采用匯編語言實現,程序簡單可讀寫性強,效率高。與傳統的電路相比,具有處理速度快、穩定性高、性價比高的優點。 參考文獻 [1]Joseph J CARR.射頻電路設計理論與應用[M].北京:電子工業出版社,2002. [2]Ken C Phkmann.數字音頻原理與應用[M]. 北京:電子工業出版社,20 02. [3]張厥勝,張會寧,邢靜.鎖相環頻率和成器[M].北京:電子工業出版社,1997. [4]余永權.ATMLE89系列單片機應用技術[M]. 北京:北京航空航天大學出版社,2002. [5]周明德.微型計算機原理及應用[M].北京:清華大學出版社,1998. [6]張迎新.單片微型計算機原理、應用及接口技術[M].北京:國防工業出版社,2003. [7]馮濤,王程.可編程邏輯器件開發技術[M].北京:電子工業出版社,2002.

提交

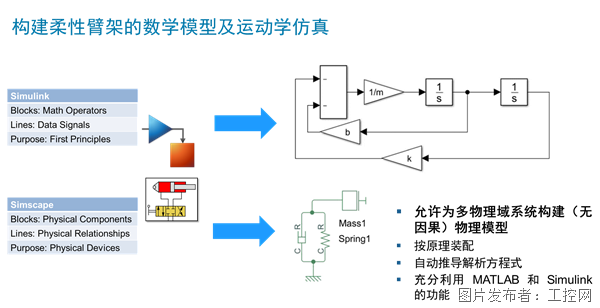

超越傳統直覺,MATLAB/Simulink助力重型機械的智能化轉型

新大陸自動識別精彩亮相2024華南國際工業博覽會

派拓網絡被Forrester評為XDR領域領導者

智能工控,存儲強基 | 海康威視帶來精彩主題演講

展會|Lubeworks路博流體供料系統精彩亮相AMTS展會

投訴建議

投訴建議